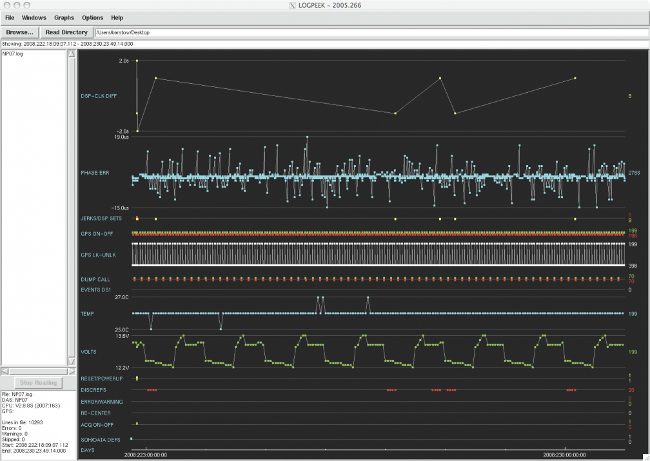

Logpeek Example Illustrating the SiRF Timing Problem

Example of LOGPEEK display of a recent RT130 logfile with a SiRF clock attached, illustrating the timing problem. Note the DSP-CLK DIFF and JERKS/DSP SETS points.

DSP CLOCK DIFFERENCE -1 SECS and 0 MSECS messages mark the beginning of timing errors in the RT130 data, due to the SiRF clock’s erroneous time shift. The SiRF goes back and forth between correct and incorrect time over periods of hours or days. The RT130, and hence your data, will follow suit, generally with a lag of 4 hours.

‘POSSIBLE DISCREPANCY’ messages will be produced whenever the SiRF and the RT130 are not in sync. Four consecutive ‘POSSIBLE DISCREPANCY’ messages will reset (JERK) the RT130 time.

If the clock is being power cycled, the clock is locking and the RT130 is phase locking with the SiRF each time it is powered, the 4-hour lag is produced.

Back to

RefTek RT130 Timing Errors Affecting PASSCAL and FA Experiments

Related categories:

- Home

- General Information

- Instrumentation

- Dataloggers

- Sensors

- All-In-One Systems

- Power Systems

- Field Procedures

- Controlled Sources

- Seismic Source Facility

- Magnetotelluric Systems at PASSCAL

- Ground Penetrating Radar

- Power and Memory Calculations Form

- Data Archiving

- Apply for a PI Account

- Experiment Scheduling

- Polar

- Important Hardware/Software Notes

- USArray

- Software